Digital System Design – Traffic Signal Controller (Verilog FSM)

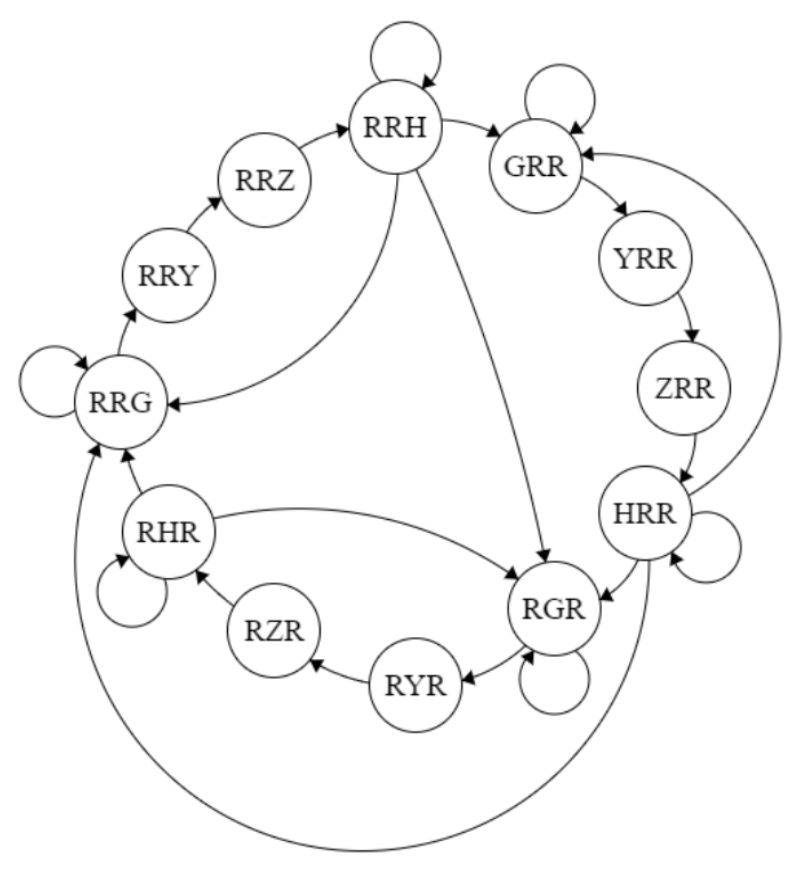

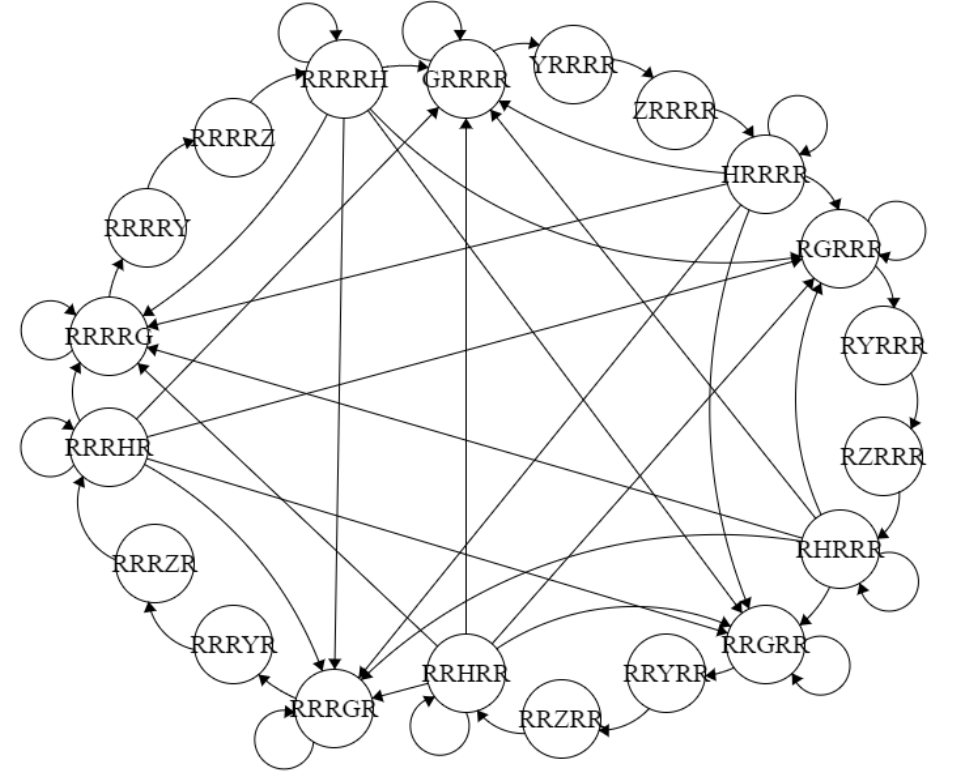

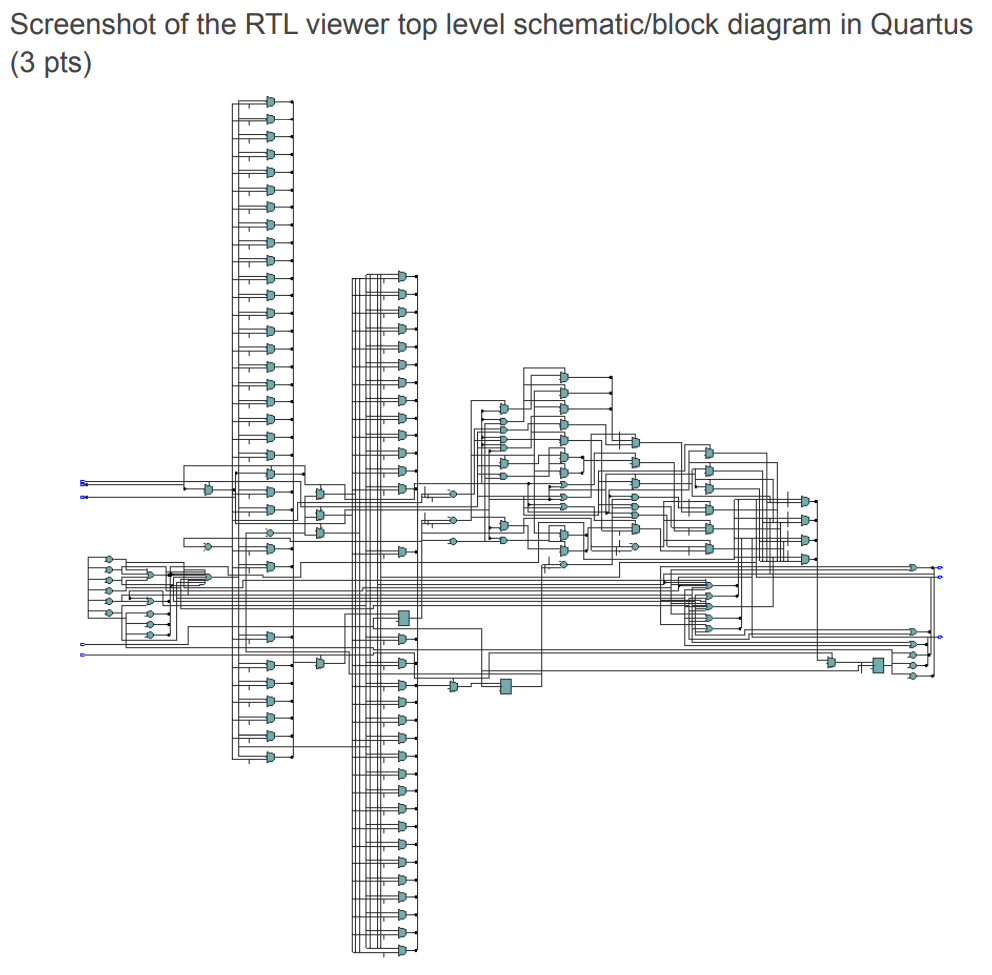

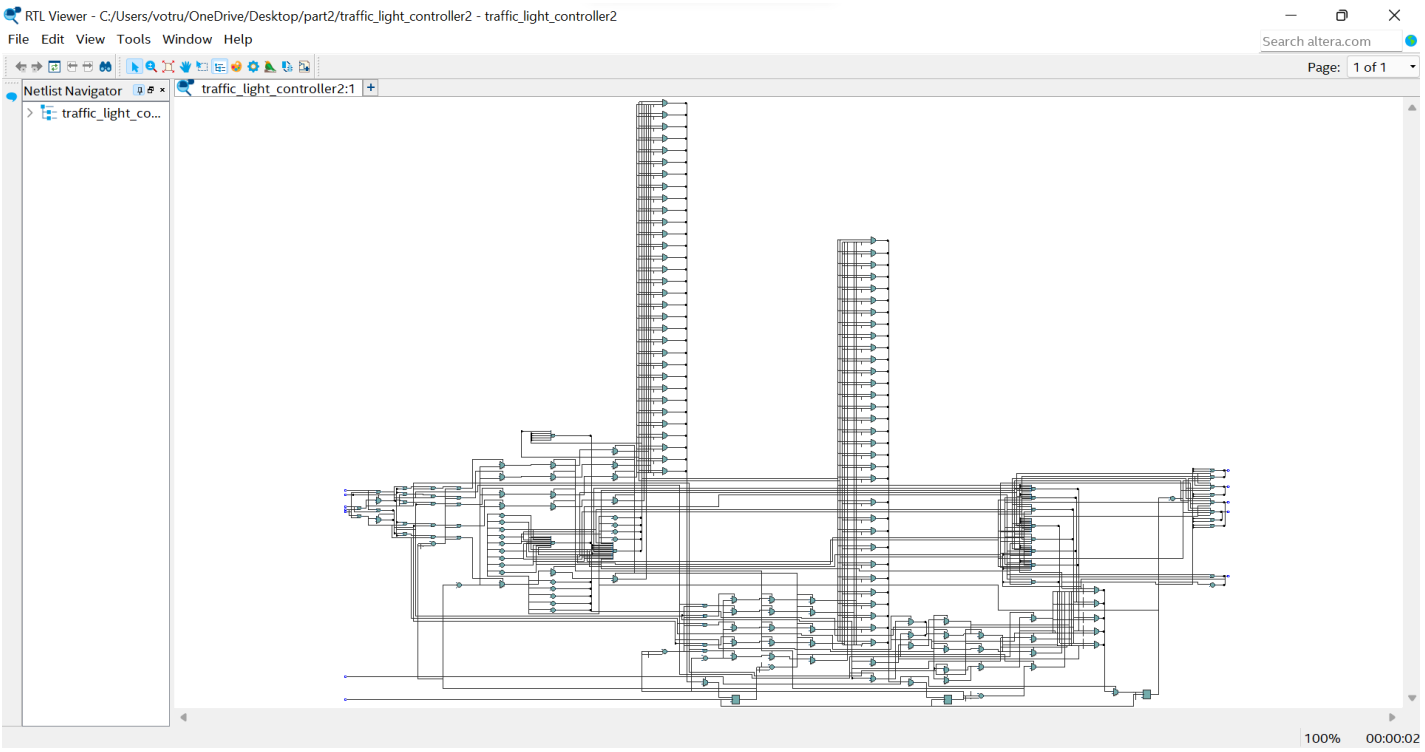

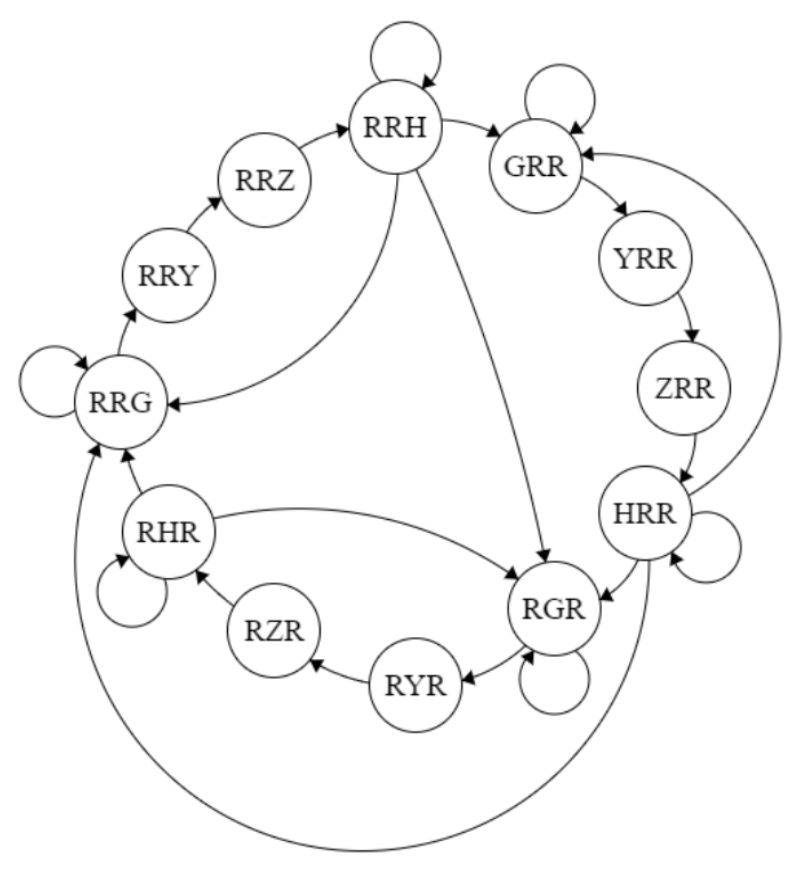

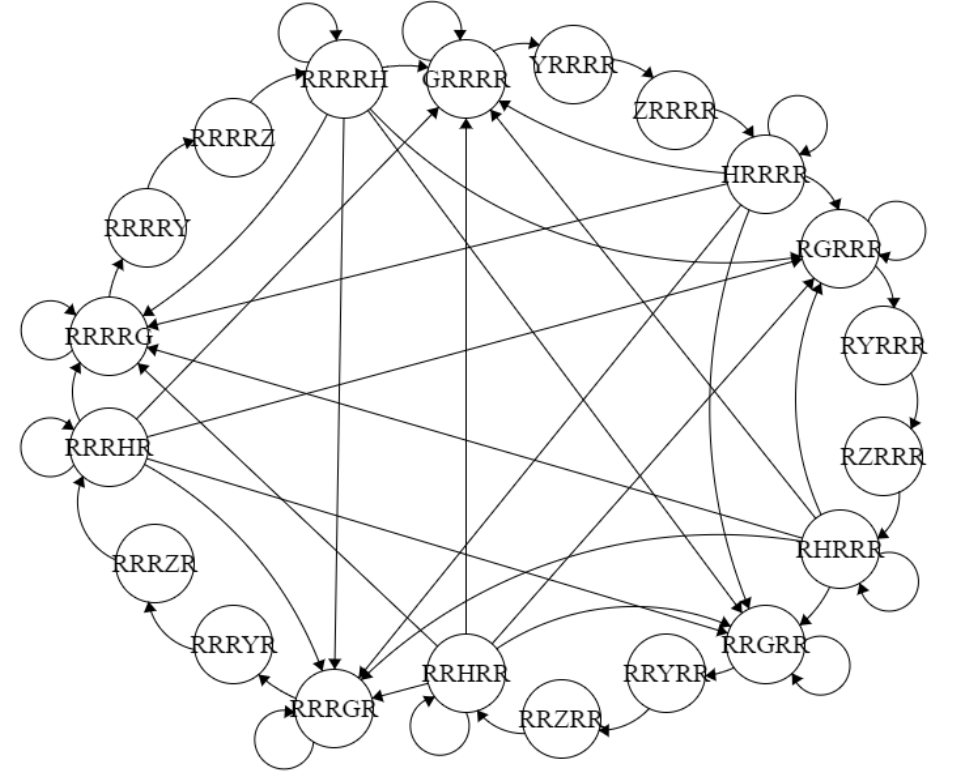

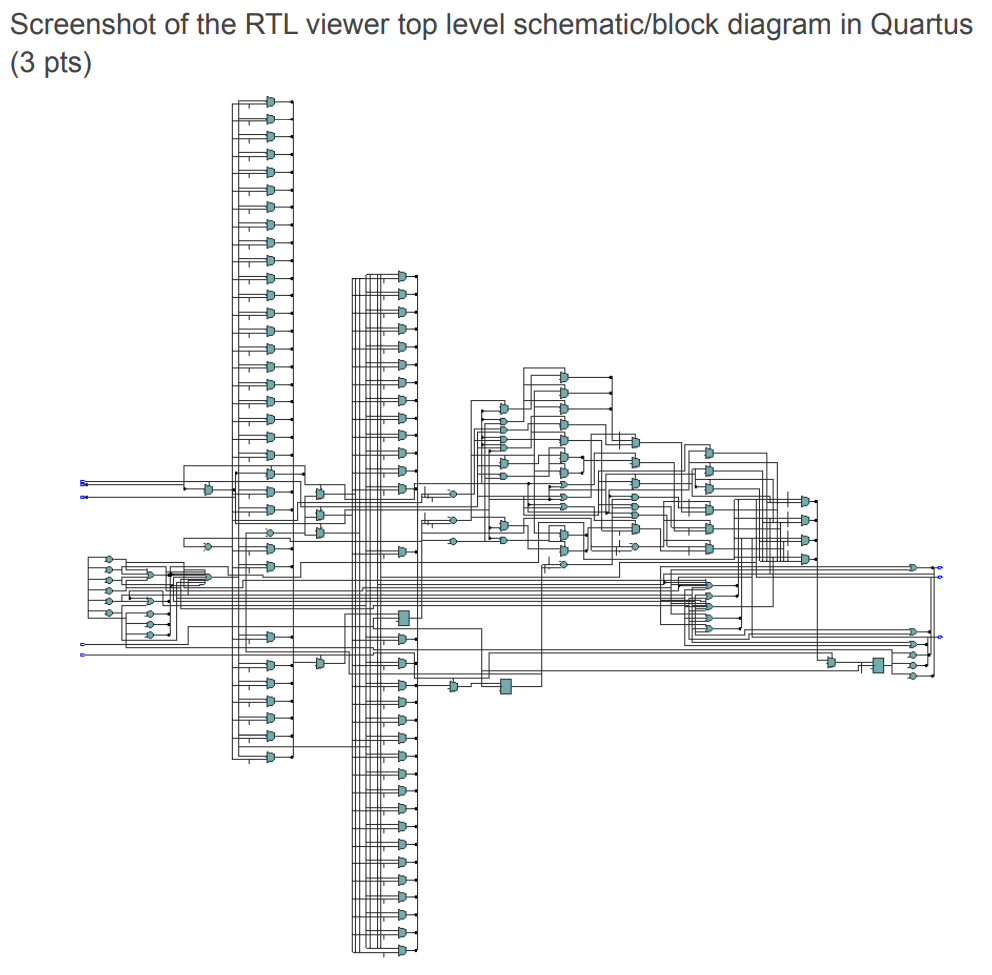

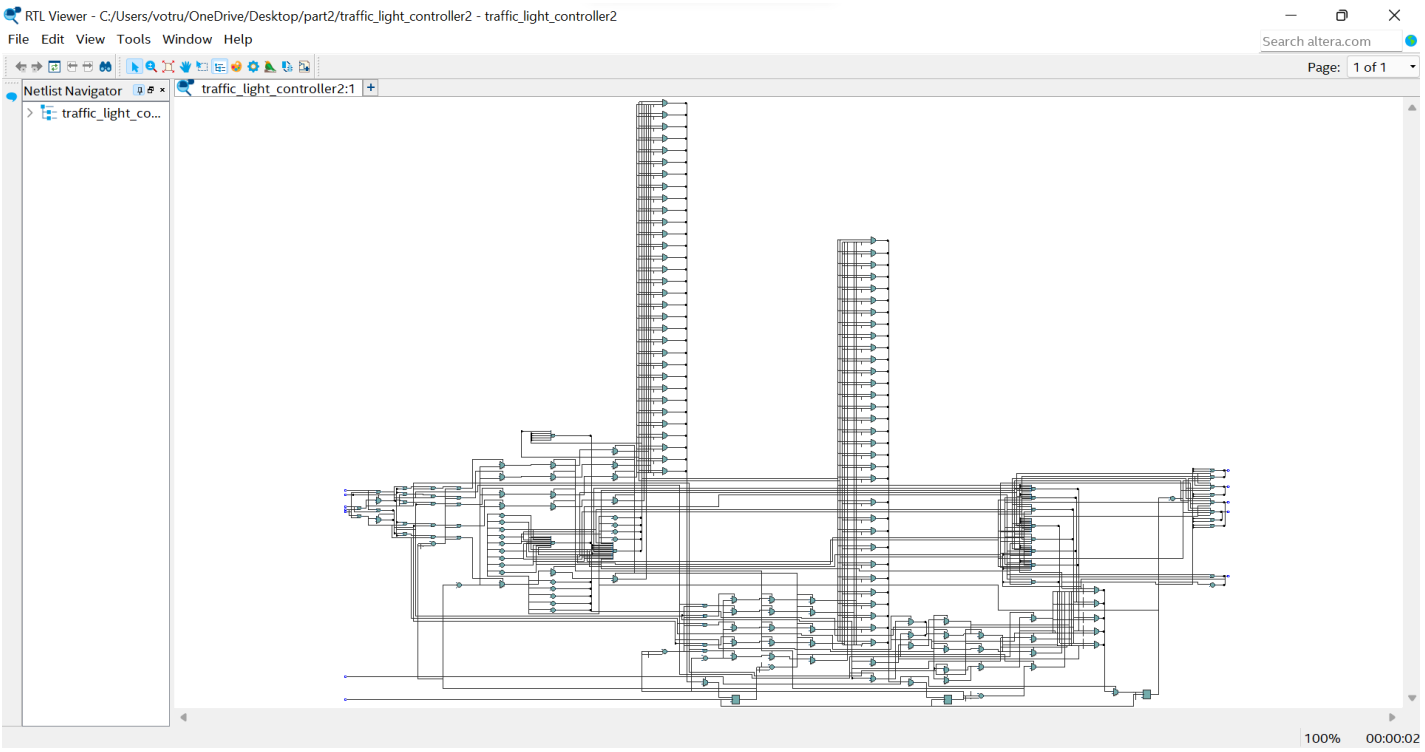

- Designed and implemented a Verilog-based state machine to control a four-way traffic system, applying logic design, FPGA-style development, and digital circuit modeling to manage timing, sequencing, and safe operations.

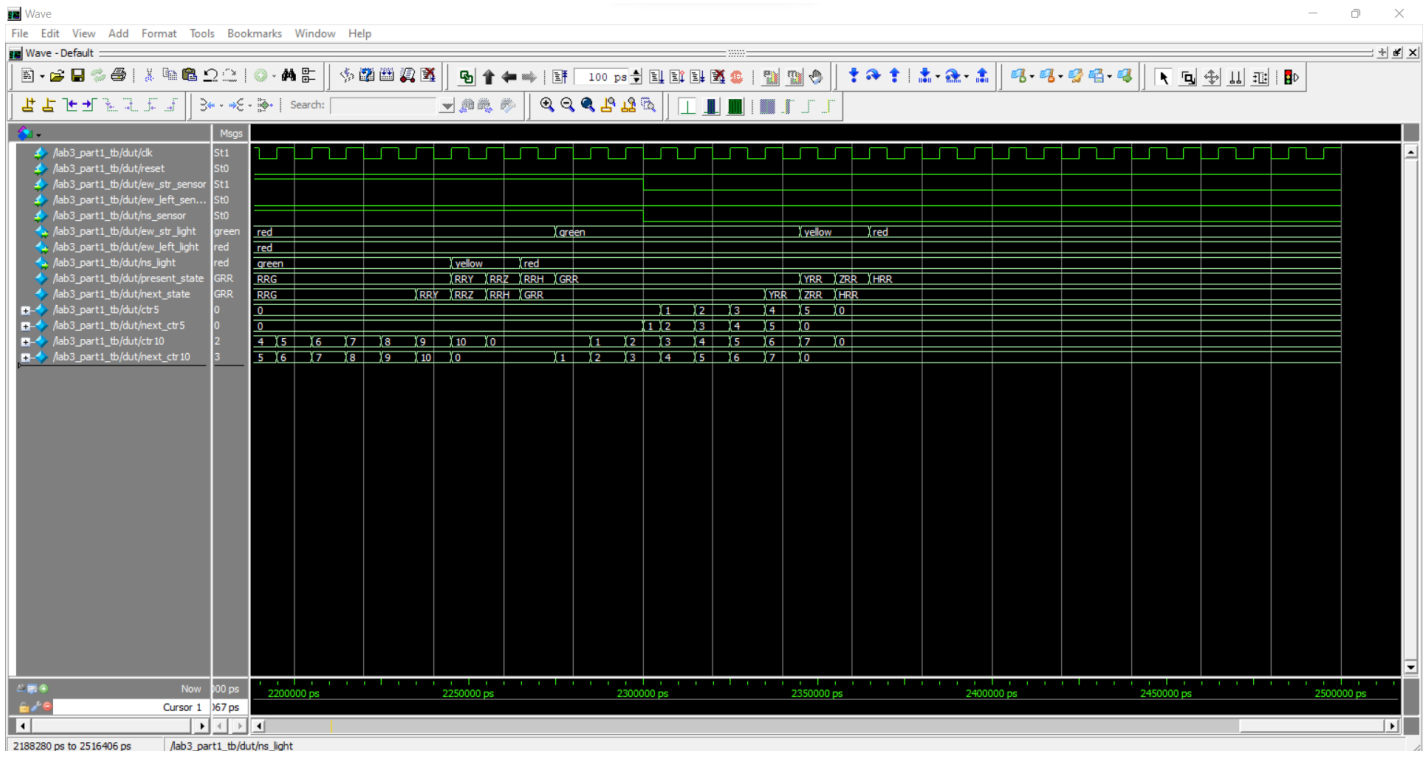

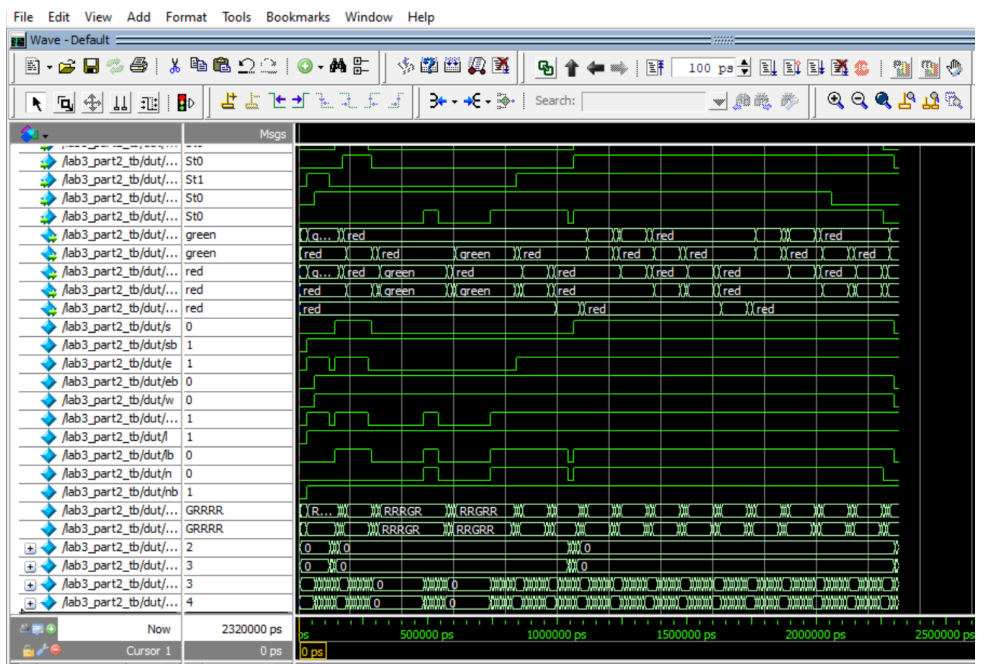

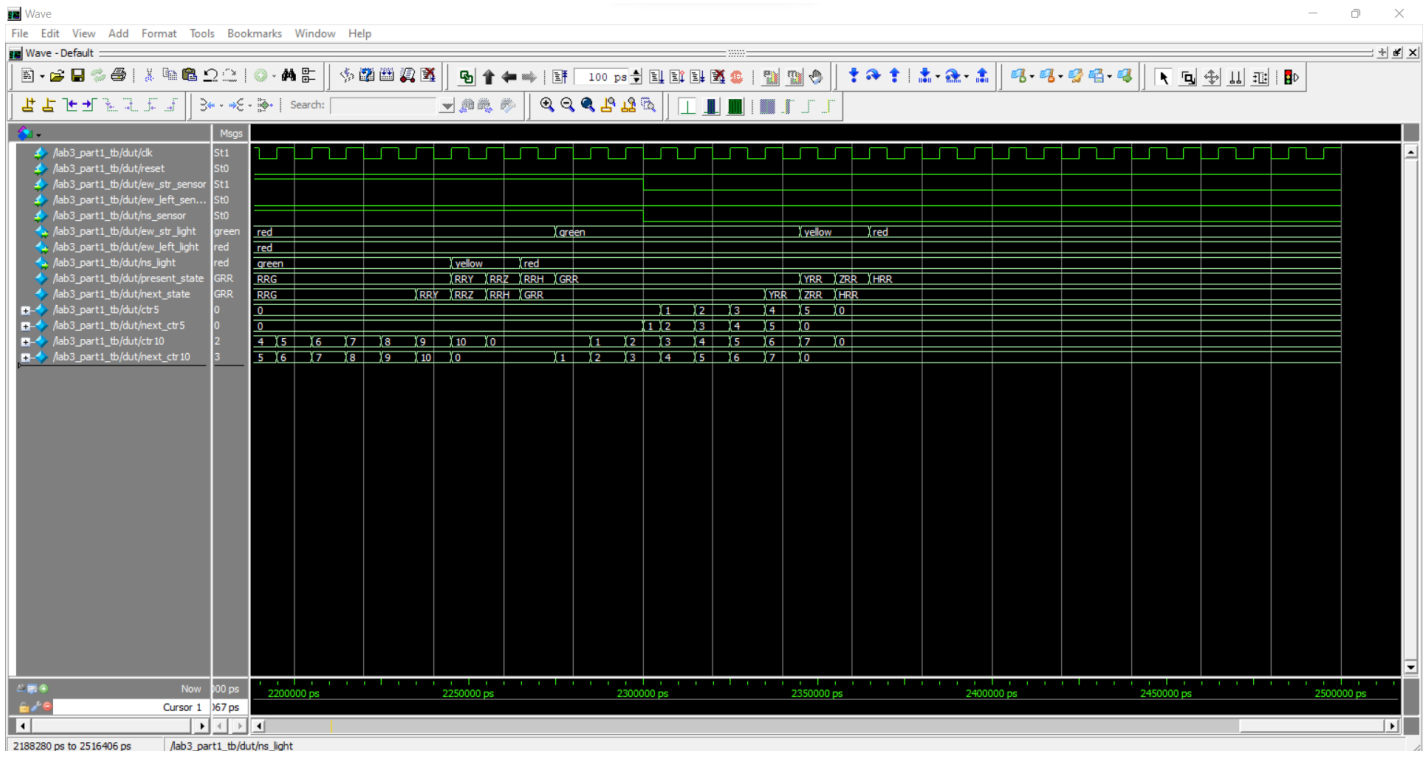

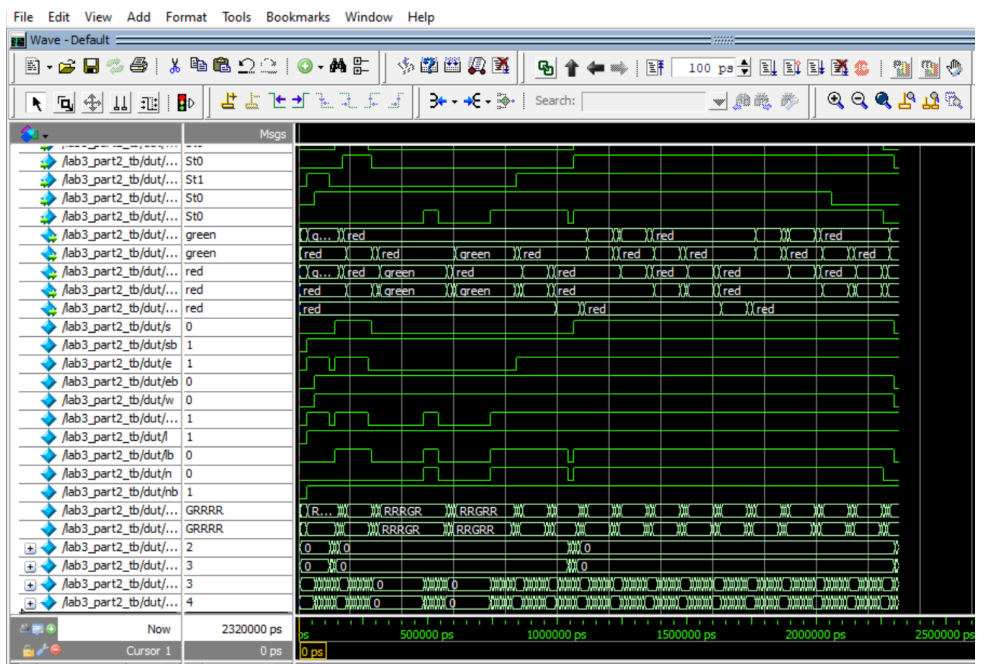

- Built and validated the system using simulation tools and test benches, performing waveform analysis to verify signal transitions and reliability, demonstrating skills in digital design, testing methodologies, and hardware verification.

Github: